MEMORIA CACHÉ

Se habla de

sistema de memoria porque en realidad nos estamos refiriendo a varios bloques:

·

El más alejado del micro y por lo tanto más lento y grande es el disco

duro. En este los datos se almacenan incluso cuando el equipo está apagado.

·

Al producirse el encendido pasan a la memoria RAM aquellos programas que

ejecutas y los datos que necesites en cada momento.

·

Por desgracia el acceso a la memoria RAM desde el micro no es

instantáneo. Esto que puede parecer algo anecdótico, estamos hablando del orden

de nanosegundos, puede provocar bloqueos y caídas de rendimiento.

Un caché es un

sistema especial de almacenamiento de alta velocidad. Puede ser tanto un área

reservada de la memoria principal con un dispositivo de almacenamiento de alta

velocidad.

La memoria caché

que se encuentra en el interior del procesador esta ideada para acelerar la

memoria RAM. La memoria caché está situada en la misma oblea de

silicio que el procesador. Es de tipo SRAM, que no necesita refrescarse frente

a las DRAM.

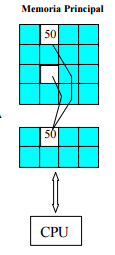

Cuando se accede por

primera vez a un dato, se hace una copia en la caché; los accesos siguientes se

realizan a dicha copia, haciendo que sea menor el tiempo de acceso medio al

dato.

Cuando el

microprocesador necesita leer o escribir en una ubicación en memoria principal,

primero verifica si una copia de los datos está en la caché; si es así, el

microprocesador de inmediato lee o escribe en la memoria caché, que es mucho

más rápido que de la lectura o la escritura a la memoria principal.

ESTRUCTURA

En el diseño de la

memoria caché se deben considerar varios factores que influyen directamente en

el rendimiento de la memoria y por lo tanto en su objetivo de aumentar la

velocidad de respuesta de la jerarquía de memoria.

UBICACIÓN

Decide dónde debe

colocarse un bloque de memoria principal que entra en la memoria caché. Las más utilizadas son:

·

Directa o Mapeado Directo (solo RAM):

al bloque i-ésimo de memoria principal le corresponde la posición i módulo n, donde n es el número de

bloques de la memoria caché. Cada bloque de la memoria principal tiene su

posición en la caché y siempre en el mismo sitio. Su inconveniente es que cada bloque

tiene asignada una posición fija en la memoria caché y ante continuas

referencias a palabras de dos bloques con la misma localización en caché, hay

continuos fallos habiendo sitio libre en la caché.

La direccion fisica de

memoria se constituye del campo correspondiente a la etiqueta, el indice (MB) y

el tamaño de la palabra.

La gran desventaja

es con el acceso. Al corresponder a varios bloques de la memoria RAM a un mismo

bloque en la cache, si un programa accede a estos datos, la cache estará

constantemente accediendo a la memoria principal para actualizar información.

·

Asociativa (Solo CAM):

Los bloques de la memoria principal se alojan en cualquier bloque de la memoria

caché, comprobando solamente la etiqueta de todos y cada uno de los bloques

para verificar acierto. Su principal inconveniente es la cantidad de comparaciones que realiza.

La

direccion fisica no hace falta el campo correspondiente a indice, ya que con el

campo etiqueta es suficiente.

Se

busca en todas las posiciones de memoria la etiqueta buscada.

Su desventaja

es la foma de busqueda: indexada y lenta, lo que indica que se debe recorrer

los bloques de la cache en busqueda del bloque de memoria deseado.

·

Asociativa por conjuntos (Híbrida RAM,CAM):

Cada bloque de la memoria principal tiene asignado un conjunto de la caché,

pero se puede ubicar en cualquiera de los bloques que pertenecen a dicho

conjunto. Ello permite mayor flexibilidad que la correspondencia directa y

menor cantidad de comparaciones que la totalmente asociativa.

La dirección física se distribuye en tres campos:

Tenemos dos vías: 2 memorias RAM, cuando se realiza la

búsqueda de la etiqueta se buscan en las dos memorias RAM y se hace la

comparación simultanea entre las 2 etiquetas que corresponden al indice y se

compara con las etiquetas buscadas.

OPTIMIZACIÓN

Para una optimización

en la manera en que se ingresa a la memoria caché y cómo se obtienen datos de

ella, se han tomado en cuenta distintas técnicas que ayudarán a que haya menos

reincidencia de fallos.

Mejorar el rendimiento.

En este aspecto el tiempo de acceso es vital, por ende

desglozando este termino tenemos:

·

Reducir

fallos en la caché (miss rate) [Tf]. Podemos controlar variables importantes

para evitar fallos

La tasa de fallos se las puede reducir con:

ü

Aumento

del tamaño del bloque

ü

Aumento

de la asociatividad

ü

Utilización

de una cache de victimas

ü

Cache

pseudoasociativas

ü

Pre-búsqueda

de instrucciones y datos (mediante buffer externos para acelerar la búsqueda)

ü

Pre-búsqueda

controladas por el compilador (del tipo Prefetch-dato que el compilador usa

para optimizar los programas luego de realizar un analisis de sus sentencias),

la pre-búsqueda se hace en paralelo con la ejecucion de las instrucciones.

ü

Optimizadores

para el compilador (Para reducir la tasa de fallos).

·

Reducir

penalizaciones por fallo (miss penalti).

Se debe priorizar los fallos de lectura frente a los

de escritura. Como los fallos se sirven leyendo bloques de Mp, una alternativa

para disminuir la penalización por fallo consiste en disminuir el tiempo de

acceso a Mp utilizando el mismo mecanismo caché, es decir, utilizando una caché

intermedia o de segundo nivel (L2) entre Mc (L1) y Mp.

·

Reducir

el tiempo de acceso en caso de acierto (hit time) [Tacierto].

Para optimizar (minimizarlo) el tiempo de acierto se

consideran 3 factores:

ü

Caches pequeñas y simples, El hardware pequeño acelera la comparación de

etiquetas y por tanto el tiempo de acierto, También hace posible su

incorporación al chip de la CPU, eliminando el conexionado externo y por tanto

el tiempo de acceso desde la CPU.

ü

Evitar traducción de direcciones durante la indexación

de las cachés, con la utilización de direcciones virtuales en las

cachés

ü

Escrituras segmentadas para rápidos aciertos de

escritura, al no ser igual

la propiedad de lectura con la de escritura ya que los aciertos de lectura son

más rápidos que los de escritura, entre otros motivos porque en los primeros se

puede leer el dato de Mc al tiempo que se comprueba si su etiqueta coincide con

la de la dirección física. Si no coincide se ignora el dato leído. Entonces para

el proceso de escritura se usa la segmentacion (pipeline) sobre la memoria

cache. De esta forma se aceleran los aciertos de escritura.

MEMORIA

PRINCIPAL

MEMORIA RAM

La memoria RAM se usa para almacenar los programas que van a ser ejecutados.

CLASIFICACIÓN DE LA MEMORIA RAM

Todas permiten operaciones de lectura/escritura. Todas son de

direccionamiento aleatorio, es decir, todas las celdas de memoria tienen el

mismo tiempo de acceso, lo cual las diferencia de las memorias de acceso

secuencial y de las de acceso directo. Todas son memorias volátiles.

RAM Estática: Es

una memoria que NO NECESITA REFRESCO. La más conocida es la SRAM (caché).

RAM Dinámica: Es

una memoria que SI NECESITA REFRESCO, ya que cada bit se almacena en una celda

formada por un transistor y un condensador y el condensador se va descargando.

La Memoria Interna

Son más lentas, pero más baratas. Durante el tiempo de refresco el

procesador no puede acceder a ellas. Son las más comunes en los ordenadores

actuales.

TIPOS DE MEMORIA RAM

VRAM, Es una memoria de propósito especial

usada por los adaptadores de vídeo. Puede ser accedida por dos diferentes

dispositivos de forma simultánea. Esto permite que un monitor pueda acceder a

la VRAM para las actualizaciones de la pantalla al mismo tiempo que un procesador

gráfico suministra nuevos datos. VRAM permite mejores rendimientos gráficos

aunque es más cara que la una RAM normal.

SIMM, es un tipo de encapsulado consistente

en una pequeña placa de circuito impreso que almacena chips de memoria, y que

se inserta en un zócalo SIMM en la placa madre. Son más fáciles de instalar que

los antiguos chips de memoria individuales, y a diferencia de ellos son medidos

en bytes en lugar de bits.

DIMM, es un tipo de encapsulado, consistente

en una pequeña placa de circuito impreso que almacena chips de memoria, que se

inserta en un zócalo DIMM en la placa madre y usa generalmente un conector de

168 contactos.

DIP, es un tipo de encapsulado consistente en

almacenar un chip de memoria en una caja rectangular con dos filas de pines de

conexión en cada lado.

RAM Disk, Se refiere a la RAM que ha sido

configurada para simular un disco duro. Se puede acceder a los ficheros de un

RAM disk de la misma forma en la que se acceden a los de un disco duro. Sin

embargo, los RAM disk son aproximadamente miles de veces más rápidos que los

discos duros, y son particularmente útiles para aplicaciones que precisan de

frecuentes accesos a disco.

SRAM, es un tipo de memoria que es más rápida

y fiable que la más común DRAM. El término estática viene derivado del hecho

que necesita ser refrescada menos veces que la RAM dinámica.

DRAM, es un tipo de memoria de gran capacidad

pero que precisa ser constantemente re-energizada o perdería su contenido. Usa

un transistor y un condensador para representar un bit, los condensadores debe

de ser energizados cientos de veces por segundo para mantener las cargas.

SDRAM entrelaza dos o más matrices de memoria

interna de tal forma que mientras que se está accediendo a una matriz, la

siguiente se está preparando para el acceso. SDRAM-II es tecnología SDRAM más

rápida esperada para 1998.

FPM, memoria en modo paginado, el diseño más común de chips de RAM

dinámica. El acceso a los bits de memoria se realiza por medio de coordenadas,

fila y columna. Antes del modo paginado, era leido pulsando la fila y la

columna de las líneas seleccionadas. Con el modo página, la fila se selecciona

solo una vez para todas las columnas (bits) dentro de la fila, dando como

resultado un rápido acceso.

EDO, es un tipo de chip de RAM dinámica que mejora el rendimiento del modo

de memoria Fast Page alrededor de un 10%. Al ser un subconjunto de Fast Page,

puede ser substituida por chips de modo Fast Page.